We are looking for highly motivated candidates to work on our projects

PhD positions below

contact : nick.barrett@cea.fr/lucia.perezramirez@cea.fr

Title : Effect of gamma-ray irradiation on ferroelectric, hafnia-based, non-volatile memory for use in extreme environments

Domain, Specialties: Material physics, surface science

Keywords: HfO2, ferroelectricity, radiation hardness, point defects, HAXPES, extreme environments

Location: Laboratory for the Study of NanoStructures and Surface Imaging (LENSIS) at CEA Saclay, France

Type of contract: PhD offer, expected start date October 2026

Description

The emergence of hafnia-based ferroelectric (FE) memories [Böscke2011] has opened a new paradigm for ultra-low-power edge computing. Hafnia is fully compatible with CMOS technology [Trentzsch2017], can be aggressively scaled [Martin2024], offers low access latency (~ns), and requires ~fJ/bit to switch—three orders of magnitude less than other emerging non-volatile memories. These properties make FE memories ideally suited for smart edge systems, overcoming the memory wall while enabling secure local data processing. Advanced 1T-1C FeRAM architectures, where the FeCAP is connected to the drain of a CMOS transistor, also provide promising paths toward NVDRAM [Micron2024] and NVSRAM [Okuno2025]. Moreover, hafnia is a by-product of the French nuclear industry giving France and Europe a major strategic advantage in global supply compared to China. These advantages align with strategic applications in space, defense, medical, nuclear safety, and heavy-duty transport, where electronics face harsh radiation environments. For example, space missions endure continuous radiation exposure for 5–15 years (hundreds of krad/year for ESA’s JUICE mission [Furano2012]), in addition to sporadic solar flare spikes. On-board systems must thus tolerate both steady-state and transient radiation doses with reliability far beyond that of consumer-grade devices. In this context, ultra-low-power FE logic and memory—especially in FD-SOI SoC implementations—could deliver up to 3× lower payload and 10× lower power consumption, while maintaining the non-volatile and radiation-hard performance required for space, defense, and nuclear applications.

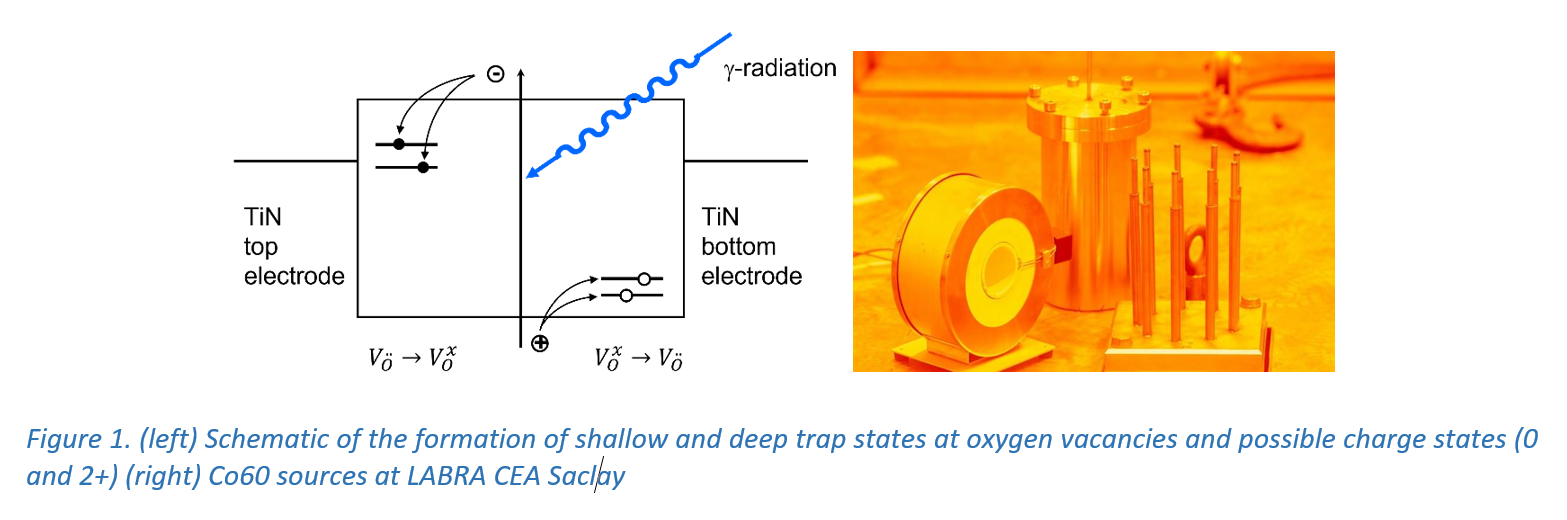

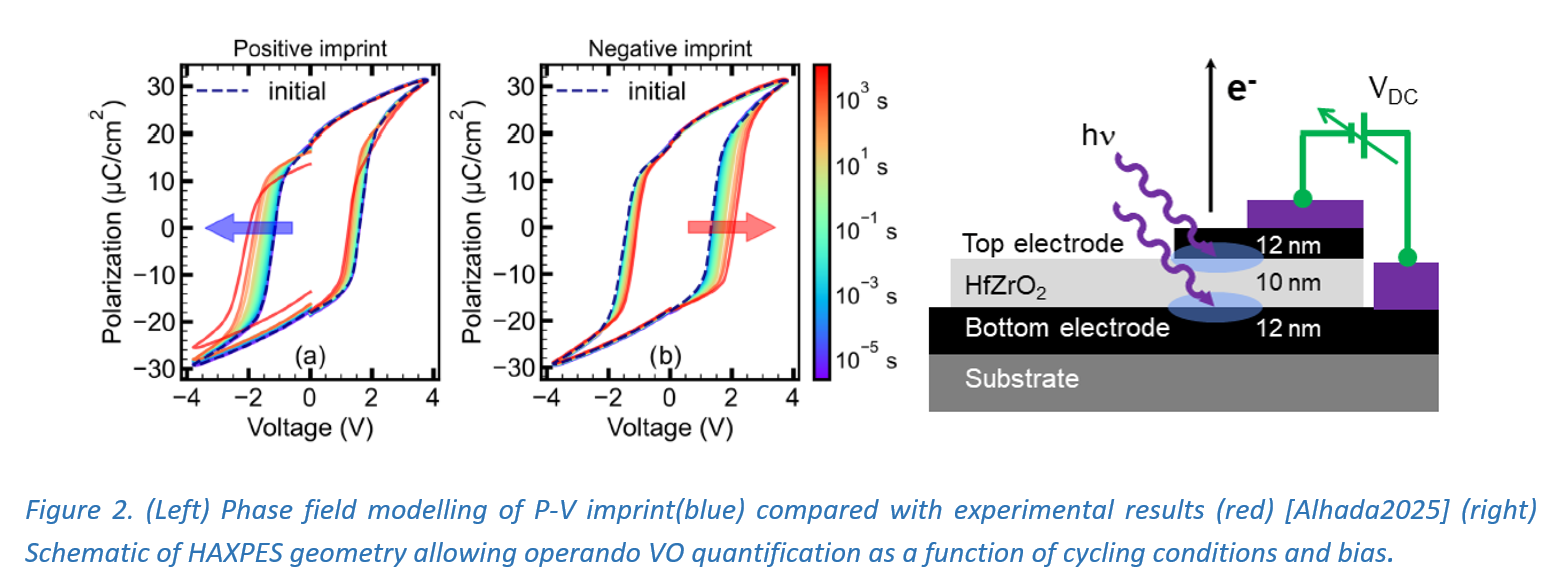

Nevertheless, stable imprint behavior still remains a significant challenge [Mikolajick2021]. Imprint induces a shift of the Polarization-Voltage (P-V) curve along the voltage axis [Alhada2025] as shown in Fig. 2 and is attributed to charge trapping/detrapping, FE domain pinning and concentration profile of charged defects. All may be accentuated under irradiation. The seminal paper of Lucovsky et al. demonstrated that the key point defect is the VO, which provides both shallow and deep charge traps, enhanced by g- and X-ray radiation [Lucovsky2006]. First detailed DFT calculations confirmed the nature of the traps at VO [Xiong2005]. Incident radiation creates e-h pairs as suggested in Fig. 1, which can then be swept to either electrode depending on the internal field or applied bias.

Ding et al reported trapped charged following generation of e-h pairs under g-ray radiation [Ding2021]. Kaya et al studied the effect of g-radiation up to 5 MRad demonstrating a high threshold voltage shift in HfO2 MOSFETs.

Radiation enhanced diffusion of defects in solids is a long-standing historical problem, originating in the need to characterize nuclear materials [Dienes1958]. Charged VO may drift under the internal polarization field in addition to the classic diffusion problem represented by Fick’s law leading to diffusion enhancement. Furthermore, VO diffusion to electrode/ferroelectric interfaces may be self-limiting, resulting in accumulation of VO in the bulk film. Trapped charge at the electrode/ferroelectric interface may further limit drift, resulting in the accumulation of excess charge in the bulk. Modest γ-radiation can degrade FeCAP polarization [Zhang2020], however, the reported resilience metrics do not include FeRAM at the memory array-level with large statistical data collection.

The correlation of radiation induced changes in VO concentration with electrical performance is an open question which will be addressed in this thesis work.

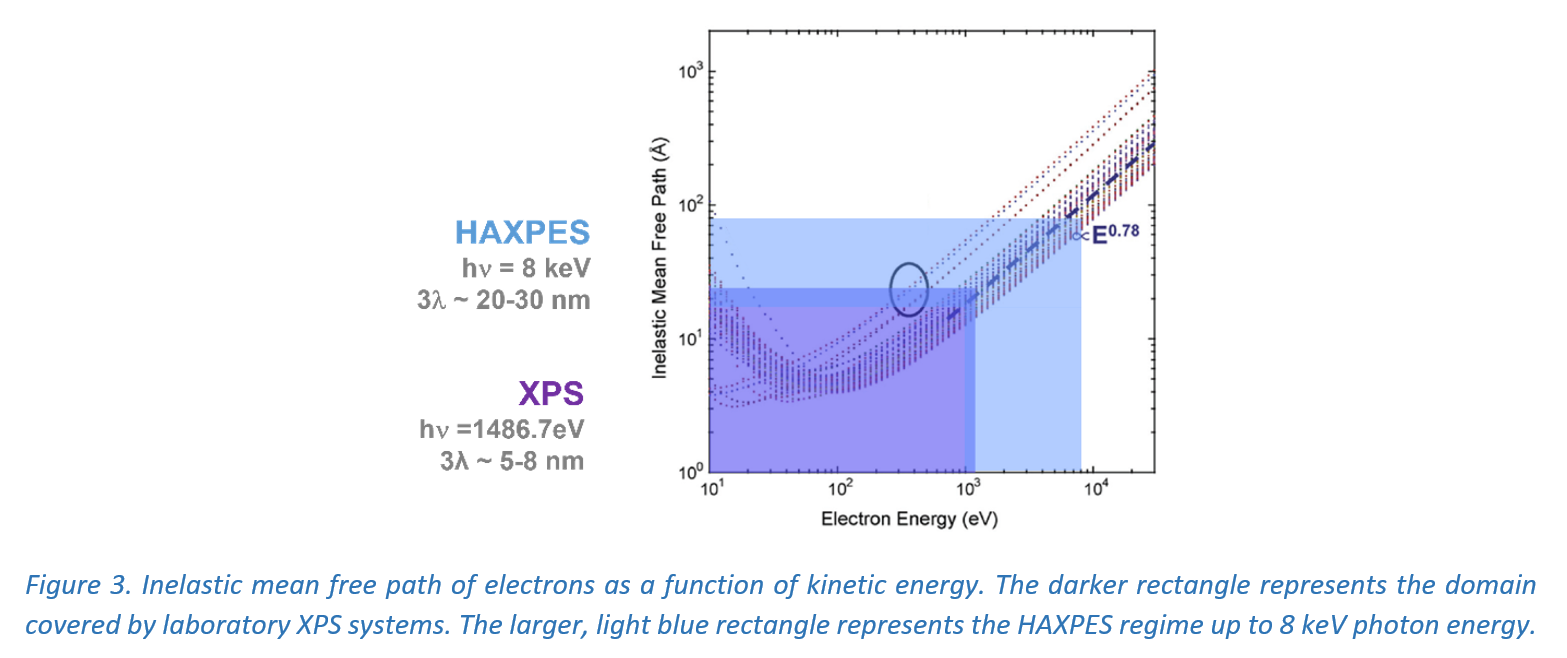

The project will use advanced photoelectron spectroscopy techniques including synchrotron radiation induced Hard X-ray photoelectron spectroscopy and complementary structural analysis including high-resolution electron microscopy, X-ray diffraction and near field microscopy. Using appropriate, low energy, ion beam etching and angular dependence of the XPS, the electrode/ferroelectric interfaces will be studied following the methods we have already developed [Hamouda2020, Hamouda2022]. Hard X-ray photoemission (HAXPES) using synchrotron radiation will be used to probe the interface chemistry and band alignment in FeCAP in a non-destructive manner (Fig. 2 (right)).

We will design samples with suitable geometry (Fig. 2) for operando measurements of the interface band line-ups as a function of the applied bias Operando experiments

There are two specific objectives to the thesis work:

1. Gamma radiation effects on HfxZr1-xO2 (HZO) material properties. Radiation induced orthorhombic to tetragonal/monoclinic/antipolar phase transitions. Generation and transport of mobile charge electron-hole pairs, charge trapping/de-trapping, enhanced VO mobility. Radiation induced point defects including VO and VHf. Radiation enhanced diffusion.

2. Quantification of FE device properties in HZO-based FeCAPs as a function of radiation dose. Outcome of the characterization will be exploited to develop and calibrate FeCAP compact models to be used at the circuit level.

The results will be compared to circuit level characterization of irradiation effect on wafer level and packaged 1T-1C 16kb and 512kb HZO-based FeRAMs, respectively. Circuit/system level simulations of irradiation. Quantification of radiation sensitivity of peripheral circuits and underlying CMOS

FeCAP fields and FeRAM circuit integrated onto 130nm CMOS test vehicles will be fabricated at CEA/Leti, Grenoble. The first task will focus on understanding the radiation induced changes in ferroelectric properties of FeCAPs. The second task will focus on the characterization of FeRAM circuit integrated on 200mm test vehicles with high statistics (at least 16kb).

The irradiations will be done at LABRA (CEA DRF) using the PAGURE irradiator allowing controlled irradiations up to 472 Gy/hr. Three campaigns are foreseen in the project, allowing to study in parallel the modifications of material properties, the FeCAP behaviour and the FeRAM and peripheral circuit response to gamma irradiation. The irradiation campaign spacing will also allow material or processing optimization between runs.

The physical and chemical analysis will be done in laboratory and synchrotron environments. X-ray and ultra violet photoelectron spectroscopy will be carried out at CEA Saclay. Hard X-ray photoemission using synchrotron radiation (Soleil, Petra-III, NSLS-2, Spring-8) will allow probing the VO concentration profile in FeCAPs [Iung2025, Yadav2025] after irradiation. XRD will probe the phase composition as a function of dose and cycling.

At each level, the experimental material and electrical characterization will be accompanied by theoretical calculations to simulate the material response to irradiation and compact modelling of the resulting device performance (collaboration with the Institut des Nanotechnologies de Lyon).

The PhD project will be carried out in the framework of a close collaboration between the CEA/Leti in Grenoble providing the samples, integrated devices and wafer scale characterization and the CEA/Iramis in Saclay for the fundamental analysis of the material properties, irradiation experiments and device scale characterizations.

Skills: Strong grounding in solid state physics is essential.

How to apply: Candidates should send a CV, cover letter and contact details for two referees to the e-mail addresses in the contact information.

Links: www.lensislab.com

iramis.cea.fr/spec/lensis

Contact

Nick BARRETT

Phone: 01 69 08 32 72

Email: nick.barrett@cea.fr

Lucia PEREZ RAMIREZ

Phone: 01 69 08 47 27

Email: lucia.perezramirez@cea.fr

References

[Böscke2011] T. S. Böscke et al., Ferroelectricity in hafnium oxide thin films Appl. Phys. Lett. 99 102903, (2011) doi: 10.1063/1.3634052

[Mikolajick2021] T. Mikolajick et al., Next generation ferroelectric materials for semiconductor process integration and their applications J. Appl Phys. 129, 100901, (2021) doi: 10.1063/5.0037617

[Alhada-Lahbabi2025] K. Alhada-Lahbabi et al., Investigating Experimental Short-Term Imprint Dynamics in Ferroelectric Hafnium Oxide Through Phase-Field Modeling Adv. Funct. Mater. (2025), e14094

[Dienes1958] G.J. Dienes and A.C. Damask Radiation Enhanced Diffusion in Solids, J. Appl. Phys. 29, 1713 (1958)

[Ding2021] M. Ding and X. Liu Damage effect of hafnium oxide gate dielectric-based metal–oxide–semiconductor structure under gamma-ray irradiation AIP Advances 11, 065304 (2021); doi: 10.1063/5.0048080

[Furano2012] G. Furano et al., Review of radiation hard electronics activities at European Space Agency Workshop on Electronics for Particle Physics 2013 IOP

[Hamouda2020] W. Hamouda et al., J. Appl. Phys. 127, 064105 (2020) https://doi.org/10.1063/1.5128502

[Hamouda2022] W. Hamouda et al., Appl. Phys. Lett. 120, 202902 (2022) https://doi.org/10.1063/5.0093125

[Iung2025] T. Iung et al., Oxygen vacancy distribution and phase composition in scaled, Hf0.5Zr0.5O2-based ferroelectric capacitors Appl. Phys. Lett. 126, 062903 (2025) doi: 10.1063/5.0245595

[Kaya2018] S. Kaya et al., Co-60 gamma irradiation effects on electrical characteristics of HfO2 MOSFETs and specification of basic radiation- induced degradation mechanism Radiation Physics and Chemistry 149 (2018) 7

[Lucovsky2006] G. Lucovsky et al., Differences Between Charge Trapping States in Irradiated Nano-Crystalline HfO2 and Non-Crystalline Hf Silicates IEEE Trans Nucl. Sci. 53, 3644 (2006)

[Martin2024] S. Martin et al., Hf0.5Zr0.5O2 FeRAM scalability demonstration at 22nm FD-SOI node for embedded applications, 2024 IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM50854.2024.10873378

[Trentzsch2017] M. Trentzsch et al. A 28 nm HKMG super low power embedded NVM technology based on ferroelectric FETs,” in IEDM Tech. Dig., Dec. 2016, pp. 11.5.1–11.5.4, doi: 10.1109/IEDM.2016.7838397

[Yadav2025] G. Yadav et al., Polarization-dependent, oxygen vacancy distribution in ferroelectric Hf0.5Zr0.5O2 capacitors IEEE 2025

[Zhang2020] W. Zhang et al., IEEE Access, 8,108121(2020), doi: 10.1109/ACCESS.2020.3000865